2057

# **Clock and Data Recovery for 10-Gb/s EPON Application**

Yonggang Tian<sup>\*</sup>, Huihua Liu and Jun Zhang

Research Institute of Electronic Science and Technology, University of Electronic Science and Technology of China, Chengdu 611731, China

**Abstract:** An integrated 10-Gb/s clock and data recovery circuit incorporates a LC-tank voltage-controlled oscillator, a half-rate binary phase detector and charge pump. On the basis of R.C.Walker's second-order model, and in accordance with jitter tolerance and jitter transfer, the minimum stability factor are derived in a view to determine the value of Cz and Rz finally. After the circuit design is accomplished in 0.13-um CMOS process, the power consumption is 210 mW from a supply voltage of 1.2V. When 10.125 Gb/s pseudorandom binary sequence is used, the jitter of the recovered clock is a peak-to-peak jitter of 8 ps.

Keywords: CDR, VCO, PD, CP, Jitter tolerance, Jitter transfer.

## **1. INTRODUCTION**

With the development of optical fiber and multimedia communication, people have higher requirements for communication quality. Among numerous Passive Optical Network architectures, 10Gbit/s Ethernet Passive Optical Network (EPON) in IEEE 802.3av protocol is one of the most popular architectures [1]. CDR is the most important module in 10G-EPON, and there are multiple approaches to completing the module function, such as PLL-Based CDR [2-4], PI-Based CDR [5], Injection Locking [6, 7], Gated VCO [8], Oversampling [9]. Among them, based on difference of PD in PLL structure, they rare divided into structures of binary phase detector [10] and linear phase detector. The former has higher gains and has inhibited periodic jitter, but due to the nonlinear structure of PD, it is difficult to analyze and design. At present, there have been two classic analysis models used to deal with CDR of this kind of structure, one of which is based on the Jri. Lee's [11, 12] piecewise linear model of large-signal, and another one is R.C. Walker's [13]  $\Delta$ - $\Sigma$ model. The former is mainly used for relatively rough estimation, while the latter can calculate the upper limit of maximum capacitance value that the module requires.

In this paper, on the basis of R.C. Walker's second-order  $\Delta$ - $\Sigma$  model, and requirements of jitter tolerance and jitter transfer in 802.3av protocol, derives the minimum stability factor and the scope of stepped frequency, then coupled with charge pump current and the gain of VCO, calculates the minimum value Cz and the resistance Rz so as to complete circuit design.

#### 2. CDR LOOP ANALYSIS

# 2.1. CDR Architecture

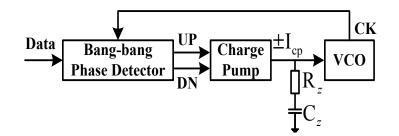

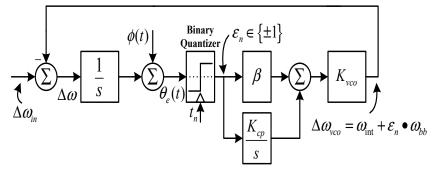

The CDR architecture includes a bang-bang PD, a charge pump, a low pass filter and an integrated LC-tank VCO, as shown in Fig. (1). The second-order CDR [13] can be rendered into a block diagram for analysis as shown in Fig. (2).  $\Delta \omega$ , is defined as the difference between the data frequency and the VCO frequency. And at the same time, the incoming data signal has a zero mean phase jitter of  $\varphi(t)$ .

It can be got from Fig. 1 that  $V_{ctrl} = I_{cp}(R_Z + 1/sC_Z) = I_{cp}R_Z + I_{cp}/sC_Z)$ , and then input voltage of VCO,  $\beta + K_{cp}/s$  can be deduced by contrasting Fig. (2), thereby

$$\boldsymbol{\beta} = \boldsymbol{I}_{cp} \bullet \boldsymbol{R}_{\boldsymbol{Z}} \tag{1}$$

$$K_{cp} = \frac{I_{cp}}{C_{7}}$$

(2)

As can be seen from the Fig. (2), it contains the integral frequency control loop and the proportional phase control loop. The output voltage of the former causes the output frequency of the VCO to be changed  $\omega_{int}$  on the basis of its free oscillation frequency. Therefore, the second - order CDR can dynamically track the change of input frequency, which broadens the frequency-locking range of CDR loop.

#### 2.2. Stability Factor

The loop phase change in one update time due to the proportional connection is  $\theta_{bb} = \omega_{bb}t_n = \beta K_{vco}t_n$ . The phase

<sup>\*</sup>Address correspondence to these authors at the Research Institute of Electronic Science and Technology, University of Electronic Science and Technology of China, Chengdu 611731, China; Tel: 1986139113; E-mail: Hunter2011@foxmail.com

Fig. (1). Half-rate CDR Architecture.

Fig. (2).  $\Delta$ - $\Sigma$  Model of second-order CDR.

change due to the integral branch is  $\theta_{int} = \int_0^{t_n} \omega_{int} dt = \int_0^{t_n} (K_{cp}t) K_{vco} dt = K_{cp} K_{vco} t_n^2 / 2$ . So the phase change in total circuit is given by

$$\theta_{\nu}(t) = \theta_{bb} + \theta_{int} = \omega_{bb}t + \frac{K_{cp}K_{\nu co}t^2}{2}$$

(3)

The ratio of these two is the stability factor of the loop

$$\xi = \frac{\theta_{bb}}{\theta_{int}} = \frac{2\beta}{K_{cp}t_n} \tag{4}$$

The integral frequency control loop has increased the risk of the stability of loop, which may result in the over-shoot of output phase  $\theta_{v}(t)$ . In order to ensure the stability of secondorder CDR loops, R. C. Walker requires as to the stability factor of the loops, and at this point, the impact of proportion circuit on the output phase  $\theta_{v}(t)$  has been predominated.

Assuming that the second-order CDR loop is locked at first, then a step signal  $\theta_{step}$  is given to the phase of the input data  $\theta_d(t)$ , and the loop can't track the change of input phase. At this moment, PD outputs 1 is continuous. Output phase  $\theta_v(t)$  in time domain is given by

$$\theta_{v}(t) = \theta_{bb} + \theta_{int} = \omega_{bb}(t + \frac{t^{2}}{\xi t_{n}})$$

(5)

The time experienced from output phase  $\theta_{v}(t)$  tacking into the input phase  $\theta_{d}(t)$  is

$$t_1 = \frac{\sqrt{1 + \frac{4\theta_{step}}{\zeta \theta_{bb}} - 1}}{2} \tag{6}$$

After  $t_1$ , as long as the proportional phase control loop plays a main role, there won't be over-shoot of phase in system, thereby

$$\omega_{\text{int}}(t_1) = \omega_{bb} \frac{2t_1}{\zeta t_n} \le \omega_{bb}$$

<sup>(7)</sup>

The minimum value of the stability factor is solved when over-shoot of phase phenomenon never occurs in system. The minimum value of the stability factor is given by

$$\zeta \ge \frac{4\theta_{step}}{3\theta_{bb}} \tag{8}$$

## 2.3. The Jitter Tolerance

According to the stability factor of the loop, R. C. Walker has derived the condition when slope overload never occurs in second-order loop

$$\omega(s) \le \omega_{bb} \left(1 + \frac{1}{s + \omega_{bb}}\right) \frac{2\omega_{bb}}{s\zeta} \tag{9}$$

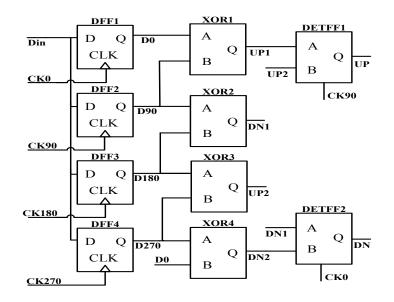

Fig. (3). Phase Detector.

Assumed that the frequency of input data does not change, but it is modulated by a sine signal in input phase  $\varphi(t)$ , and the input phase  $\varphi(t) = m_j \sin(2\pi f_j t_n + \varphi_j)$  is namely sine jitter. Where  $m_j$  is amplitude of sinusoidal jitter;  $f_j$  is the frequency of jitter;  $\varphi_j$  is its initial phase. Supposed that the condition of the jitter tolerance is that slope overload doesn't occur in system, it can be obtained that

$$m_{j} \bullet s \mid_{s=j2\pi f_{j}} \le \omega_{bb} (1 + \frac{1}{s+\omega}) \frac{2\omega_{bb}}{s\xi}$$

$$\tag{9}$$

Generally speaking,  $|s| >> 2/\xi$ , equivalently, by

$$\boldsymbol{\omega}_{bb} \ge \boldsymbol{m}_i \bullet 2\pi \boldsymbol{f}_i \tag{10}$$

## 2.4. The Jitter Transfer

When slope overload doesn't occur in the system, the output phase of the second-order CDR loop can accurately track the change of input phase. Similarly, assume that the slope overload just occur in the system, the loop bandwidth is namely the bandwidth of jitter transfer,  $BW_{JT} = \omega_{bb_{-}JT} / 2\pi m_j$ . Based on the fact that the loop bandwidth of design circuit is required to be smaller than the bandwidth of the jitter transfer curve, can be derived that

$$\omega_{bb} \le BW_{JT} 2\pi m_j \tag{11}$$

## **3. CIRCUIT DESIGN**

#### 3.1. Phase Detector

Phase detector can be classified into linear PDs and Binary PDs. Because the former generate a linearly proportional output with phase error, it is less suitable for high speed circuit. Binary PDs only care about the phase lead or the phase lag, producing a positive or negative value at their output. Therefore, a half-rate binary PD was applied. The block diagram of the phase detector circuit is shown in Fig. (3). The data rate of CDR arrives to 10Gbps, so the DFF and other high speed parts were both implemented in current mode logic (CML).

PD received four clock signals from PLL. D0, D90 and D180 constitute the first set of sampling data three times in succession, and after exclusive-OR gate of XOR1 and XOR2, UP1 and DN1 signal outputted respectively. The signals of UP2 and DN2 are outputted in the same way. Double edge trigger (DEFF) is composed of two flip-latches and a demultiplexer, and solved the error of output because of signal delay. Finally, UP is outputted by signals of UP1 and UP2 after passing through DEFF1, while DN is outputted by signals of DN1 and DN2 after passing through DEFF2. Because operations of separate half-rate clock signals of CK0 and CK90 are implemented twice on DEFF1 and DEFF2 in one clock period, the updated frequency of their output signal of UP and DN is exactly the same as the full rate of Alexander phase discriminator.

#### 3.2. Charge Pump

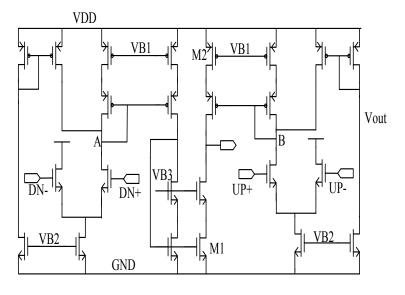

Fig. (4) shows the implementation of the differential charge pump. To be robust against supply and substrate noise, differential architecture was chosen. The entire same discharge and charge circuit is achieved by symmetric pump circuit. When the signal of DN+ or UP+ change from open state to closed state, parasitic capacitance of points of A and B causes slower rise of their electrical level, slowing down the operating speed of the circuit. A current mirror with smaller current value can be added to avoid this situation.

When the CDR is locked, the PD circuit generates no pulses, the filter capacitance is discharged by the impedances of the current sources and by currents caused by current source mismatches. To reduce both effects, the cascode current sources are used, at the same time, M1 and M2 need to

Fig. (4). Charge pump.

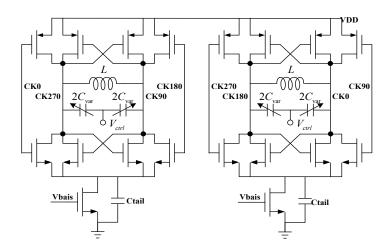

Fig. (5). Schematic of VCO.

choose a large dimension. The variations of Vth may result in current source mismatches and Vth are roughly proportional to the square root of the gate area. So a large gate area can reduce current mismatch.

#### 3.3. Loop Filter

The performance of CDR loop is decided by loop filter. Through the above analysis of CDR second-order loop, and according to the jitter requirements by agreement, stepped frequency  $\omega_{bb}$  and stability factor  $\zeta$ , coupled with the current  $I_{cp}$  of CP and the gain  $K_{vco}$  of VCO can be obtained. By  $\omega_{bb} = \beta K_{vco} = I_{cp} R_z K_{vco}$  and  $\zeta = \theta_{bb} / \theta_{int} = 2\beta / K_{cp} t_n$ , the parameters of the loop filter are given by

$$R_z = \frac{\omega_{bb}}{I_{cp}K_{vco}}$$

(12)

$$C_z = \frac{\zeta t_n}{2R_z} \tag{13}$$

## 3.4. VCO

The design of the VCO directly impacts the jitter performance and the reproducibility of the CDR circuit. A ring oscillator is an easy design and low-cost, but it is difficult to achieve a potentially lower jitter. To reduce phase noise, LC topologies was applied.

Fig. (5) shows the implementation of the QVCO. Cross coupling of PMOS and PMOS transistor is conducted, which has reduced the tail current of QVCO and the power consumption of the circuit when start-oscillating condition is satisfied. At the same time, rising edge of output waveform is more symmetrical with its falling edge, because the PD is half rate, Parallel-coupled can achieve the clock output of quadrature phase. A capacitance is connected in parallel with

Fig. (6). Simulated Current mismatch of CP.

Fig. (7). Simulated Phase Noise of VCO.

tail current source to reduce the amplitude of even-order harmonic.

# 4. SIMULATION RESULT

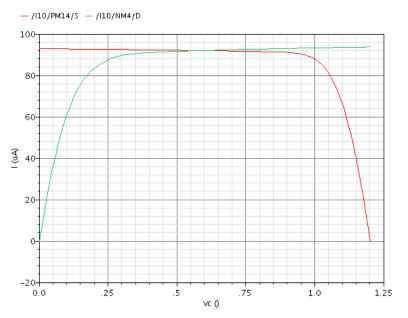

The CDR circuit has been designed in a 0.13 um CMOS process. The circuit mismatch of charge pump is shown in Fig. (6). The CP output voltage increased from 0.43V to 0.78V when mismatch current is less than 1uA.

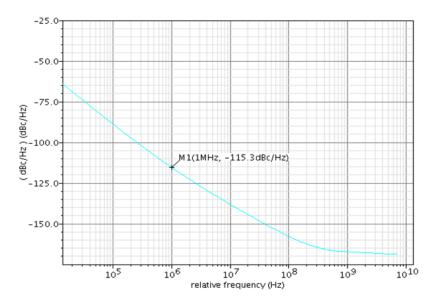

VCO is an extremely significant module in CDR, and its jitter performance is directly related to the recovered data. The simulation curve of phase noise of VCO is shown in Fig. (7), when the center frequency is 5.1 GHz, the phase noise at 1 MHZ is -115.3dBc/Hz.

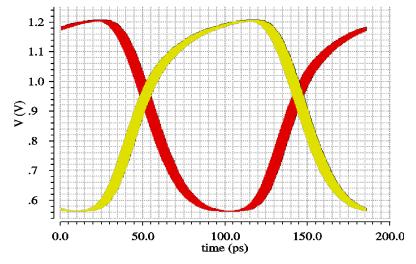

The CDR was simulated with a pseudo-random bit sequence (PRBS) of length  $2^{23} - 1$ . The rate of input data is 10 G/s. The eye diagram of clock signal recovered by CDR is as shown in Fig. (8), with a peak - to - peak jitter of 8ps.

# CONCLUSION

Low-cost, low-power, and high-integration issues make CMOS the preferred technology for high-speed optical communication circuits. A 10-Gb/s clock and data recovery

Fig. (8). Simulated recovered clock.

circuit designed in 0.13-u m CMOS technology performs phase locking, data regeneration.

# **CONFLICT OF INTEREST**

The authors confirm that this article content has no conflicts of interest.

#### ACKNOWLEDGEMENTS

Declared none.

# REFERENCES

- K. Tanaka, A. Agata, and Y. Horiuchi, "IEEE 802.3av 10G-EPON Standardization and Its Research and Development Status," J. Journal of Lightwave Technology, vol. 28, no. 4, pp. 651-661, 2010.

- [2] Bindra, H.S., Chatterjee, S., Saha, K., and Kukal T., "Clock and Data Recovery module in 90nm for 10Gbps Serial Link with -18dB channel attenuation," J. IEEE International Symposium on Circuits and Systems, pp. 2472 - 2475, 2013.

- [3] K. Fukuda, "A 12.3-mW 12.5-Gb/s Complete Transceiver in 65-nm CMOS Process," J. IEEE Journal of Solid-State Circuits, vol. 45, no. 12, pp. 2838-2849, 2010.

- [4] Shita Guo, Tianzuo Xi, Guoying Wu, Tianwei Liu, Tao Zhang, Ping Gui, Yanli Fan, and Morgan, M., "A low-power 28 Gb/s CDR using artificial lc transmission line technique in 65 nm CMOS," C.2014 IEEE 57<sup>th</sup> International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 85-88, 2014.

- [5] Kalantari, N., and Buckwalter J.F., "A Multichannel Serial Link Receiver With Dual-Loop Clock-and-Data Recovery and Channel

Received: June 16, 2015

Revised: August 10, 2015

Accepted: September 19, 2015

© Tian et al.; Licensee Bentham Open.

This is an open access article licensed under the terms of the (https://creativecommons.org/licenses/by/4.0/legalcode), which permits unrestricted, non-commercial use, distribution and reproduction in any medium, provided the work is properly cited.

Equalization," J. IEEE Transactions on Circuits and Systems, Vol. 60, no. 11, pp. 2920-2931, Nov 2013.

- [6] Shuli Geng, Ni Xu, Jun Li, Xueyi Yu, Woogeun Rhee, and Zhihua Wang, "A PLL/DLL Based CDR with ΔΣ Frequency Tracking and Low Algorithmic Jitter Generation," J. IEEE International Symposium on Circuits and Systems, pp.1179 1182, 2013.

- [7] Fan-Ta Chen, Jen-Ming Wu, Liu, J.Y.-C., and Chang, M.-C.F., "A 100Gb/s Quad-rate Transformer-Coupled Injection Locking CDR Circuit in 65nm CMOS," J. IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1950-1953, 2013.

- [8] Ming-Chiuan Su, Wei-Zen Chen, Pei-Si Wu, Yu-Hsian Chen, Chao-Cheng Lee, and Shyh-Jye Jou, "A 10Gbps, 1.24pJ/bit, Burst-Mode Clock and Data Recovery with Jitter Suppression," C. IEEE Custom Integrated Circuits Conference (CICC), pp.1-4, 2013.

- [9] Jia-An Jheng, Wei-Sung Chang, and Tai-Cheng Lee, "A 3Xoversampling hybrid clock and data recovery circuit with programmable bandwidth," J. International Symposium on VLSI Design, pp. 1-4, 2014.

- [10] Byoung-Joo Yoo, Woo-Rham Bae, Jiho Han, Jaeha Kim, and Deog-Kyoon Jeong, "Linearization Technique for Binary Phase Detectors in a Collaborative Timing Recovery Circuit," J. IEEE Transactions On Very Large Scale Integration Systems, pp. 1-12, 2013.

- [11] J. Lee, "Modeling of Jitter in bang-bang Clock and Data Recovery Circuits," C. IEEE Custom Integrated Circuit Conference, pp. 711-714, 2003.

- [12] J. Lee, "Analysis and Modeling of bang-bang Clock and Data Recovery Circuits," J. IEEE Journal of Solid-State Circuits, vol. 39, no. 9, pp. 1571-1580, 2004.

- [13] R. C. Walker, "Designing bang-bang PLLs for Clock and Data Recovery in Serial Data Transmission System," *J. IEEE Press*, pp. 34-45, 2003.